## GIMIX™ 2 PORT RS-232C SERIAL INTERFACE for the SS50(C) 30 pin I/O bus

#### FEATURES

- \* TWO SEPARATE RS-232 PORTS (W/HANDSHAKE) ON A SINGLE BOARD

- \* JUMPER PROGRAMMABLE CONNECTOR PINOUTS (DCE/DTE)

- \* INDIVIDUAL BAUD RATE AND INTERRUPT JUMPERS FOR EACH PORT

- \* CAN BE USED WITH 4 OR 16 DECODED ADDRESSES PER I/O SLOT

- \* OPTIONAL CABLE SETS ALLOW DIRECT PLUG-IN OF STANDARD RS-232 CABLES AND CONNECTORS

- \* USES TWO 6850 ACIAS

A ADDDECCEC

\* GUARANTEED 2MHz. OPERATION

### HARDWARE CONFIGURATION

#### ADDRESS DECODING

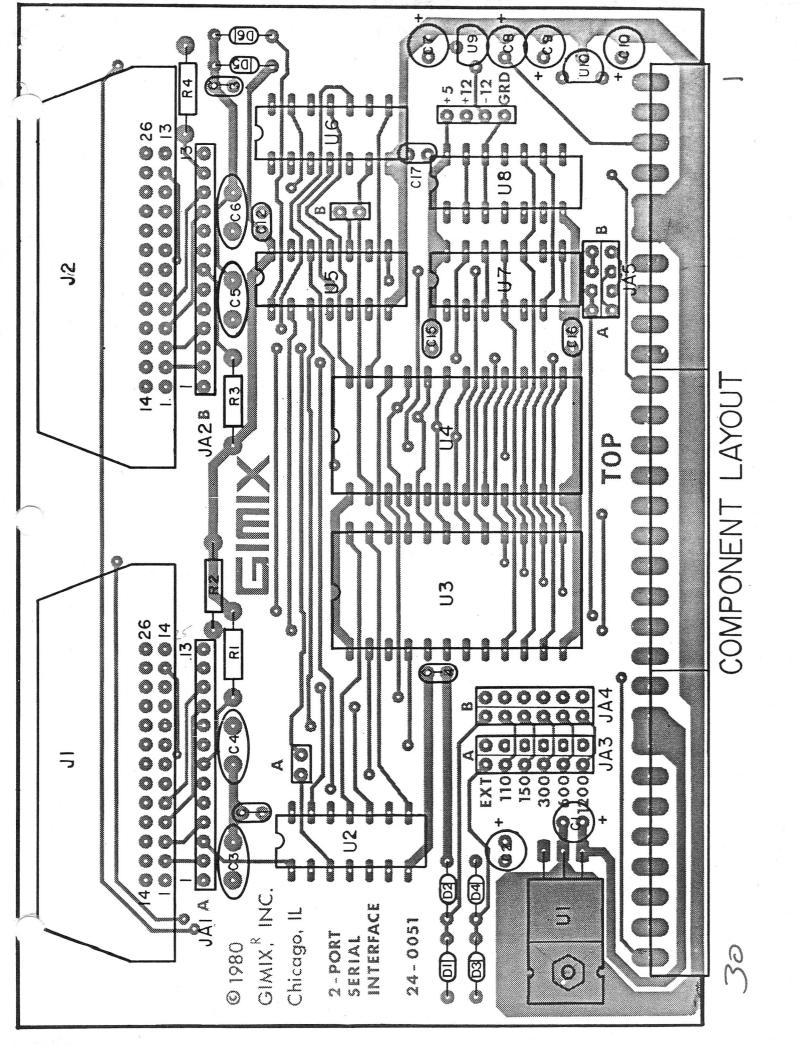

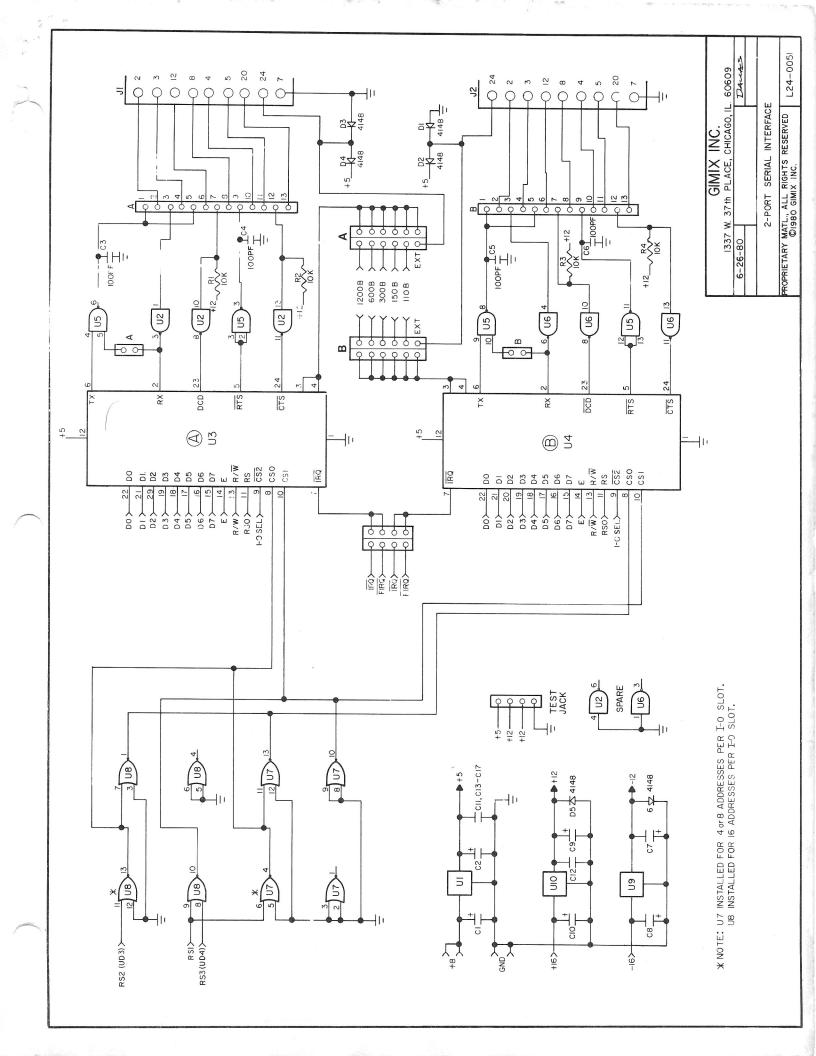

The board can be configured for systems with either 4 or 16 decoded addresses per I/O slot by changing the location of the 74LS02 I.C. (U-7 or U-8). If the 74LS02 is installed at location U-7, the board is configured for 4 addresses per I/O slot. To configure the board for 16 addresses per I/O slot, the 74LS02 must be installed at location U-8. (see the component layout drawing for the locations of U-7 and U-8) When configured for 16 addresses per slot, the board decodes two additional lines, RS2/UD3 and RS3/UD4.

Each of the two ACIAs, U-3('A' side) and U-4('B' side), occupy 2 bytes of the available address space, one for its control port and one for its data port. The following table shows the locations of the ports for both the 4 address per slot and the 16 address per slot configurations:

| 4 ADDRESSES             | 16 ADDRESSES   |        |         |

|-------------------------|----------------|--------|---------|

| 'LS02' at U-7           | 'LS02' at U-8  |        |         |

|                         |                |        |         |

| \$XXXX U-3(A) CONTROL   | \$XXX0         | U-3(A) | CONTROL |

| \$XXXX+1 U-3(A) DATA    | \$XXX1         | U-3(A) | DATA    |

| \$XXXX+2 U-4(B) CONTROL | \$XXX2         | unused |         |

| \$XXXX+3 U-4(B) DATA    | \$XXX3         | unused |         |

|                         | \$XXX4         | U-4(B) | CONTROL |

| w 8 "                   | <b>\$XXX</b> 5 | U-4(B) | DATA    |

| \$XXXX = BASE ADDRESS   | \$XXX6         | unused |         |

| OF I/O SLOT             | •              | "      |         |

|                         | •              | "      |         |

|                         | •              | 11     |         |

|                         | \$XXXF         | unused |         |

\$XXX0 = BASE ADDRESS OF I/O SLOT

16 ADDDECCEC

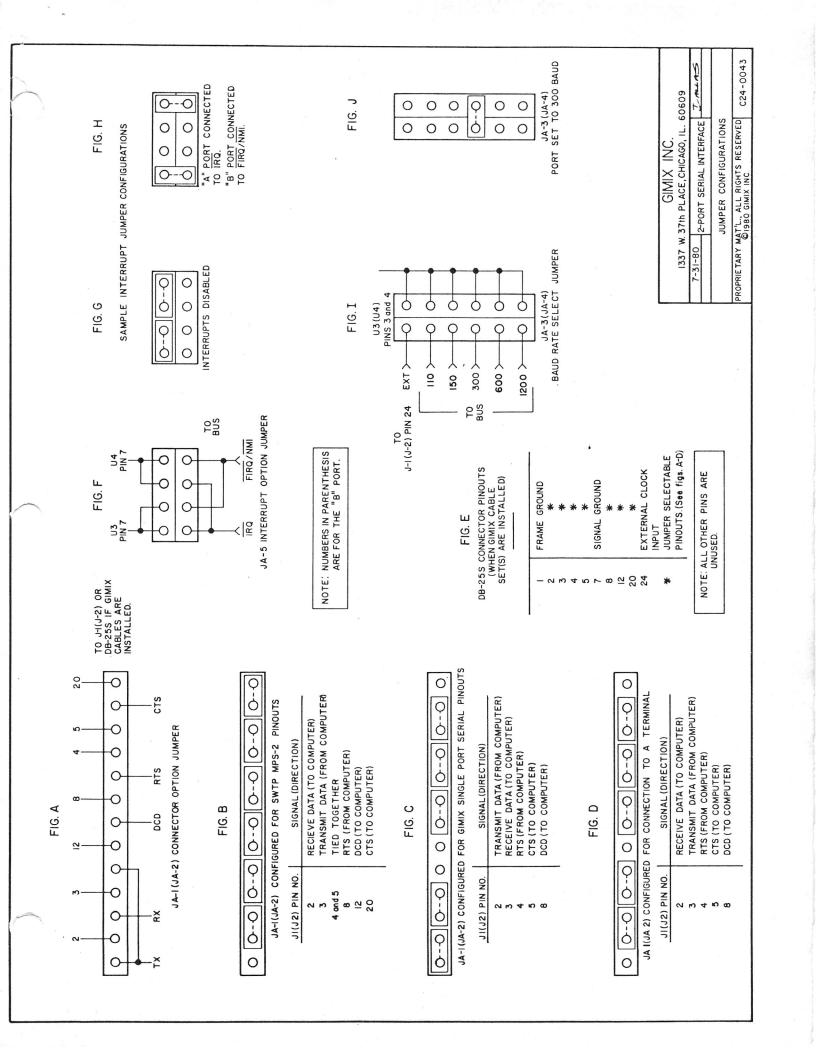

Figure 'A' of the JUMPER CONFIGURATIONS drawing shows the pinouts of jumper areas JA-l and JA-2. These jumpers are used to configure the pinouts of the I/O connectors, J-l for the 'A' side and J-2 for the 'B' side, as required by the external device(s) being connected. The numbers at the top of the figure correspond to the pin numbers of the 25 pin 'D' type connector when GIMIX cable sets are used. Pins 1, 7, and 24 are permanently defined as FRAME GROUND, SIGNAL GROUND, and EXTERNAL CLOCK INPUT respectively (see figure 'E' of the JUMPER CONFIGURATION drawing).

Figures 'B', 'C', and 'D' show three common jumper configurations and their corresponding pinouts. Consult the documentation for the device(s) being connected, to determine the necessary signals and their corresponding pinouts. Figures 'B' and 'D' are most commonly used when connecting the board to a terminal or other device configured like a terminal (RS-232 Data Terminal Equipment/DTE). Figure 'C' is used when connecting to a modem or other device configured like a modem (RS-232 Data Communications Equipment/DCE).

In many cases, especially at slow baud rates, the handshake signals (CTS, DCD, and RTS) are not required. In these cases a simple three wire cable, with connections to pins 2, 3, and 7, is all that is required. Internal pull-up resistors on the handshake inputs (DCD and CTS) permit them to be left open (unconnected), when their use is not required, without affecting the operation of the system. When any of the handshake signals are not used, the corresponding jumper(s) should be removed from the board or connected to an unused (unconnected) pin(s) to prevent possible interference from other signals which may be present on the cable from the external device.

## BAUD RATE SELECT JUMPERS (JA-3 AND JA-4)

Jumper areas JA-3 and JA-4 are used to select the baud rate for the 'A' and 'B' sides respectively. Each side can be connected to any one of the five baud rate lines of the 30 pin bus or to an external baud rate input on pin 24 of the I/O connector. Figure 'I' of the JUMPER CONFIGURATION drawing shows the pinouts of JA-3 and JA-4. The baud rate designations shown are the standard designations for the 30 pin bus baud rate lines. The actual baud rate(s) available on these lines will depend on the configuration of the system baud rate generator. Consult the documentation for the baud rate generator to determine the available baud rates or to configure one of the lines for a specific rate. Figure J shows the proper jumper position for connection to the 300 baud line.

If the baud rate clock is to be provided by an external source, such as a terminal or modem, the baud rate jumper(s) must be set to the EXT (external) position and the clock signal connected to pin 24 of the I/O connector. NOTE: The external clock input MUST BE A TTL LEVEL (0 to +5 Volt) signal. Although the EXT inputs are diode protected, application of signal levels outside the 0 to +5V. range may damage the diodes and/or the ACIA(s).

## INTERRUPT OPTION JUMPER (JA-5)

The interrupt outputs from each of the ACIAs can be individually connected to either of the two interrupt lines of the 30 pin bus (IRQ or NMI/FIRQ). Figure 'F' of the JUMPER CONFIGURATION drawing shows the pinout of JA-5. When used with systems that do not require interrupts from the I/O devices , the interrupt jumpers should be installed as shown in figure 'G' (interrupts disabled). This is the standard configuration for use with GMXBUG-09/GIMIX FLEX™. When used with operating systems that require I/O device interrupts, such as OS-9™ or UniFLEX, jumpers should be installed to connect the interrupt outputs to the proper bus line, IRQ or NMI/FIRQ, as required by the operating system. Consult the software vendor's documntation to determine the interrupt. Note: The interrupt available on the required designated NMI/FIRQ will depend on the type of system the configuration of the mother board. See the mother board and/or board documentation.

# HALF-DUPLEX JUMPERS (A and B)

Two additional jumper areas, labeled 'A' and 'B' on the circuit board and COMPONENT LAYOUT drawing, can be used to configure the board for half-duplex operation. If a jumper(s) are installed at these locations, the data input (RX) for the associated side is connected to the data output (TX) and the data received by the board is automatically re-transmitted to the transmitting device (terminal, modem, etc.). In most applications, the full-duplex mode is used and these jumpers should be left OPEN (unconnected).